Journal of Mechanical Engineering and Sciences (JMES)

ISSN (Print): 2289-4659; e-ISSN: 2231-8380 Volume 10, Issue 1, pp. 1895-1907, June 2016 © Universiti Malaysia Pahang, Malaysia

# Optimization of process parameter variations on leakage current in SOI vertical double gate MOSFET device

K.E. Kaharudin<sup>1\*</sup>, F. Salehuddin<sup>1</sup>, A.S.M. Zain<sup>1</sup> and M.N.I. Abd Aziz<sup>1</sup>

<sup>1</sup>Centre for Telecommunication Research and Innovation, Faculty of Electronics and Computer Engineering, Universiti Teknikal Malaysia Melaka (UTeM), Hang Tuah Jaya, Durian Tunggal, 76100 Melaka, \*Email: khairilezwan@yahoo.com.my

Phone: +6094246239; Fax: +6094246222

#### **ABSTRACT**

This paper presents a study of optimizing input process parameters on leakage current ( $I_{OFF}$ ) in a silicon-on-insulator (SOI) Vertical Double-Gate (DG) Metal Oxide Field-Effect-Transistor (MOSFET) by using the L36 Taguchi method. The performance of the SOI Vertical DG-MOSFET device is evaluated in terms of its lowest leakage current ( $I_{OFF}$ ) value. An orthogonal array (OA), main effects, signal-to-noise ratio (SNR) and analysis of variance (ANOVA) are utilized in order to analyse the effect of input process parameter variation on the leakage current ( $I_{OFF}$ ). Based on the results, the minimum leakage current (( $I_{OFF}$ ) of the SOI Vertical DG-MOSFET is observed to be 0.009 nA/ $\mu$ m or 9 pA/ $\mu$ m while keeping the drive current ( $I_{ON}$ ) value at 434  $\mu$ A/ $\mu$ m. Both the drive current ( $I_{ON}$ ) and leakage current ( $I_{OFF}$ ) values yield a higher  $I_{ON}/I_{OFF}$  ratio (48.22 x 10 $^6$ ) for low power consumption application. Meanwhile, the polysilicon doping tilt angle and polysilicon doping energy are recognized as the most dominant factors, contributing factor effects percentages of 59% and 25% respectively.

Keywords: Analysis of variance; DG-MOSFET; SNR; SOI.

## **INTRODUCTION**

The Metal Oxide Semiconductor Field-Effect-Transistor (MOSFET) with silicon-on-insulator (SOI) technology has been widely studied due to its superb device performance. The SOI technology has been proven to suppress short channel effects (SCE) and thus improve the drive current ( $I_{ON}$ ). The drive current ( $I_{ON}$ ) is an important response to determine the driving capability of the MOSFET device. However, the leakage current ( $I_{OFF}$ ) is still an important response to be controlled in order to obtain a higher  $I_{ON}/I_{OFF}$  ratio. The high  $I_{ON}/I_{OFF}$  ratio will lead to lower power consumption of the device. Therefore, in pursuing the excellent characteristics of the SOI vertical DG-MOSFET device, the drive current ( $I_{ON}$ ) must be ensured to be large while keeping the leakage current ( $I_{OFF}$ ) as low as possible.

Leakage current ( $I_{OFF}$ ) is measured during the switch-off condition of the device. In other words, it is a value of drain current ( $I_D$ ) when there is no gate voltage ( $V_G$ ) applied [1]. Normally, as the device shrinks, the leakage current ( $I_{OFF}$ ) will be higher. High leakage current ( $I_{OFF}$ ) in nano-scale regimes is becoming a significant contributor to the power dissipation of the MOSFET device [2]. This increase in  $I_{OFF}$  is typically due to the charge-sharing effect caused by drain-induced barrier lowering (DIBL) or due to deep

channel punchthrough currents [3]. As the channel width decreases, both the threshold voltage ( $V_{TH}$ ) and leakage current ( $I_{OFF}$ ) will be modulated by the width of the transistor, giving rise to a significant narrow-width effect. All these adverse effects will cause a threshold voltage ( $V_{TH}$ ) reduction (leakage current increase), especially in very small-scale devices [2]. Many factors are believed to make a large contribution to the rise of the leakage current ( $I_{OFF}$ ) value. One of the most recognized factors is known as process parameter variations. The input process parameters such as the  $V_{TH}$  implant dose,  $V_{TH}$  implant energy, polysilicon tilt angle, S/D implant energy, etc. need to be optimized in order to obtain a robust design. A lot of input process parameters have to be studied in order to identify the most significant factors that influence the leakage current ( $I_{OFF}$ ) value.

This paper attempts to describe the optimization of input process parameters for a minimum value of leakage current (IOFF) in the SOI Vertical DG-MOSFET device. The responses of a certain design can be optimized by modelling the input process parameters [2]. Sixteen input process parameters are involved in the analysis, which are the substrate implant dose, V<sub>TH</sub> implant dose, V<sub>TH</sub> implant energy, V<sub>TH</sub> implant tilt, polysilicon doping dose, polysilicon doping energy, polysilicon doping tilt, halo implant dose, halo implant energy, halo implant tilt, S/D implant dose, S/D implant energy, S/D implant tilt, compensation implant dose, compensation implant energy and compensation implant tilt. Due to this large number of input process parameters, an orthogonal array of L<sub>36</sub> is selected for this analysis. The well-known statistical method known as the Taguchi method is utilized in this analysis. The Taguchi approach provides a practical design strategy in which a modified design of experiment (DOE) is introduced. This technique emphasizes reducing the number of experimental runs, but still increasing the efficiency. In the present study, there is a mixed matrix of 16 input process parameters with 3 levels and 2 noise factors with 2 levels involved. There would be as many as 172,186,884 (316x22) runs of experiments if using the conventional full factorial design. The experiment will take only 144 runs with the Taguchi method. Therefore, the Taguchi method is capable of helping the designer to study the effect of many factors in the most economical way.

A special orthogonal array consisting of 36 rows and 4 columns is constructed in order to retrieve 144 samples of results. This orthogonal array is used for a design of experiment (DOE) that could assist the designer to study varations of multiple process parameters in a fast and economical way. The signal-to-noise ratio (SNR) is utilized in order to analyse the data and then to determine the optimal combination of process parameters [4]. There are three categories of performance characteristics in the analysis of SNR, which are known as nominal-the-best, lower-the-better and higher-the-better [5].

The SNR of each level of input process parameters is computed based on signal-to-noise (S/N) analysis. Regardless of the category of the performance characteristic, a larger SNR corresponds to a better performance characteristic [6]. Therefore, the optimal level of the process parameters is the level with the highest SNR. In addition, a statistical analysis of variance (ANOVA) is conducted to observe which process parameters are statistically dominant and significant. With the SNR and ANOVA analysis, the optimal combination of the process parameters can be accurately predicted [7, 8]. Finally, a confirmation experiment is performed to verify the optimal process parameters obtained from the Taguchi analysis. Therefore, the Taguchi method is utilized to obtain the optimal process parameters for a lower Ioff value of the device.

## MATERIALS AND METHODS

SILVACO Technology Computer Aided Design (TCAD) tools are utilized to aid in designing and optimizing the input process parameters. SILVACO TCAD tools consist of two modules which are ATHENA and ATLAS. The ATHENA module was used for process simulation in the device's design, while the ATLAS module was used for device simulation and characterization.

## **Process and Device Structure**

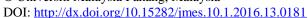

The process began with a selection of a P-type silicon with <100> orientation as the main substrate. The initial silicon was then doped with boron with a concentration of 1 x  $10^{14}$ atom/cm<sup>3</sup>. The formation of BO<sub>X</sub> was done by depositing 40 nm oxide thickness (t<sub>BOX</sub>). The silicon thickness (tsi) was about 4 nm. The silicon was dry-etched in order to form a pillar or ridge to separate the two gates. The height of the silicon pillar of 140 nm was preferred in order to provide the effective channel length (Leff) of 79 nm. The simulation process was followed by the gate oxidation process at a temperature of 875° C. The thickness of the gate oxide is an essential parameter in the vertical dimension which will determine the gate control. The next step was to dope substrate ions, which were boron, into the silicon with a concentration of 3.81 x 10<sup>11</sup> atom/cm<sup>3</sup> at an energy level of 10 keV and tilt angle of 7°. This step is important in order to vary the threshold voltage (V<sub>TH</sub>) of the vertical DG-MOSFET device. The next simulation process was to deposit polysilicon on top of the gate oxide. Then, the polysilicon and polysilicon oxide were etched away to form a polysilicon gate. The gate was made of polysilicon because of its ability to prevent source/drain ions from penetrating into the channel region. A layer of oxide was oxidized on top of the polysilicon deposition at a temperature of 880 C°. A phosphor dosage of 1 x 10<sup>18</sup> atom/cm<sup>3</sup> was then dipped into the polysilicon gate at an energy level of 20 keV and tilt angle of 10°. This is done in order to increase the conductivity of the polysilicon since polysilicon is a low conductivity metal. The conductivity of the gate would affect the switching frequency of the transistor.

In order to get the optimum performance for the Vertical DG-MOSFET device, indium with a dosage of 1.17 x 10<sup>13</sup> atom/cm<sup>3</sup> was doped at an energy level of 170 keV and tilt angle of 24°. Halo implantation was followed by depositing sidewall spacers. The sidewall spacers were then used as a mask for source/drain implantation. An arsenic atom with a concentration of 1.25 x 10<sup>18</sup> atom/cm<sup>3</sup> at an energy level of 45 keV and tilt angle of 80° was implanted to ensure the smooth current flow in the Vertical DG-MOSFET device. Compensation implantation is utilized later by implanting a phosphor dosage of 2.51 x 10<sup>12</sup> atom/cm<sup>3</sup> at an energy level of 63 keV and tilt angle of 7°. This step is taken in order to reduce parasitic effects that could lower the current. Next, silicide (CoSi) was formed at the top of the source and drain region by sputtering cobalt on the silicon surface. This transistor was then connected with aluminium metal. The aluminium layer was deposited on top of the Inter-Metal Dielectric (IMD) and unwanted aluminium was etched to develop the contacts [9, 10]. The procedure was completed after the metallization and etching were performed for the electrode formation, and the bonding pads were opened. It is important to use the same level of process parameters for Vertical DG-MOSFET devices both with and without SOI in order to investigate their performance. The final SOI Vertical DG-MOSFET device structure was completed by mirroring the right-hand side structure. The completed structure of the SOI Vertical DG-MOSFET device is illustrated in Figure 1. Once the devices were built with ATHENA, the complete devices could be simulated in ATLAS to provide specific characteristics such as the subthreshold

drain current  $(I_D)$  versus gate voltage  $(V_G)$ . The off-state leakage current  $(I_{OFF})$  can be extracted from that curve.

Figure 1. SOI Vertical DG-MOSFET device structure.

| Table 1. | Input | process | parameters | and | their | levels. |

|----------|-------|---------|------------|-----|-------|---------|

|----------|-------|---------|------------|-----|-------|---------|

| Symbol       | Process Parameter              | Unit                 | Level 1               | Level 2               | Level 3               |

|--------------|--------------------------------|----------------------|-----------------------|-----------------------|-----------------------|

| A            | Substrate Implant Dose         | atom/cm <sup>3</sup> | $1 \times 10^{14}$    | $1.03 \times 10^{14}$ | -                     |

| В            | V <sub>TH</sub> Implant Dose   | atom/cm <sup>3</sup> | $3.78 \times 10^{11}$ | $3.81 \times 10^{11}$ | -                     |

| C            | V <sub>TH</sub> Implant Energy | keV                  | 10                    | 12                    | -                     |

| D            | $ m V_{TH}$ Implant Tilt       | degree               | 7                     | 10                    | 13                    |

| $\mathbf{E}$ | Polysilicon Doping Dose        | atom/cm <sup>3</sup> | $3.60 \times 10^{14}$ | $3.63 \times 10^{14}$ | $3.66 \times 10^{14}$ |

| $\mathbf{F}$ | Polysilicon Doping Energy      | keV                  | 20                    | 22                    | 24                    |

| G            | Polysilicon Doping Tilt        | degree               | 7                     | 10                    | 13                    |

| H            | Halo Implant Dose              | atom/cm <sup>3</sup> | $1.17 \times 10^{13}$ | $1.20 \times 10^{13}$ | $1.23 \times 10^{13}$ |

| J            | Halo Implant Energy            | keV                  | 170                   | 172                   | 174                   |

| K            | Halo Implant Tilt              | degree               | 24                    | 27                    | 30                    |

| $\mathbf{L}$ | S/D Implant Dose               | atom/cm <sup>3</sup> | $1.22 \times 10^{18}$ | $1.25 \times 10^{18}$ | $1.28 \times 10^{18}$ |

| M            | S/D Implant Energy             | keV                  | 43                    | 45                    | 47                    |

| N            | S/D Implant Tilt               | degree               | 74                    | 77                    | 80                    |

| O            | Compensation Implant           | atom/cm <sup>3</sup> | $2.51 \times 10^{12}$ | $2.54 \times 10^{12}$ | $2.57 \times 10^{12}$ |

|              | Dose                           |                      |                       |                       |                       |

| P            | Compensation Implant           | keV                  | 61                    | 63                    | 65                    |

|              | Energy                         |                      |                       |                       |                       |

| Q            | Compensation Implant Tilt      | degree               | 7                     | 10                    | 13                    |

# Taguchi Orthogonal L<sub>36</sub> Array Design

The objective of the present study was to determine the optimal level of 16 input process parameters, i.e. substrate implant dose,  $V_{TH}$  implant dose,  $V_{TH}$  implant energy,  $V_{TH}$  implant tilt, polysilicon doping dose, polysilicon doping tilt, halo implant dose, halo implant tilt, S/D implant dose, etc. Each of these was represented by letters A, B, C, D,

E, F, G, H, J, K, L, M, N, O, P and Q. Two levels of the first 3 input process parameters and three levels of the other 13 input process parameters were selected as shown in Table 1.

Table 2. Noise factors and their levels.

| Symbol | Noise factor                      | Unit    | Level 1 | Level 2 |

|--------|-----------------------------------|---------|---------|---------|

| U      | Gate oxidation temperature        | Co      | 875     | 878     |

| V      | Polysilicon oxidation temperature | $C^{o}$ | 877     | 880     |

Table 3. Experimental layout using  $L_{36}$  orthogonal array.

| Exp no.  |   |   |        |     |        | Pro    | cess | Parai | mete | r Lev  | els    |        |        |   |     |        |

|----------|---|---|--------|-----|--------|--------|------|-------|------|--------|--------|--------|--------|---|-----|--------|

| •        | A | В | С      | D   | Е      | F      | G    | Н     | J    | K      | L      | M      | N      | О | P   | Q      |

| 1        | 1 | 1 | 1      | 1   | 1      | 1      | 1    | 1     | 1    | 1      | 1      | 1      | 1      | 1 | 1   | Q<br>1 |

| 2        | 1 | 1 | 1      | 1   | 2      | 2      | 2    | 2     | 2    | 2      | 2      | 2      | 2      | 2 | 2   | 2 3    |

| 3        | 1 | 1 | 1      | 1   | 3      | 3      | 3    | 3     | 3    | 3      | 3      | 3      | 3      | 3 | 3   |        |

| 4        | 1 | 2 | 2      | 1   | 1      | 1      | 1    | 1     | 2    | 2      | 2      | 2      | 3      | 3 | 3   | 3      |

| 5        | 1 | 2 | 2      | 1   | 2      | 2      | 2    | 2     | 3    | 3      | 3      | 3      | 1      | 1 | 1   | 1      |

| 6        | 1 | 2 | 2      | 1   | 3      | 3      | 3    | 3     | 1    | 1      | 1      | 1      | 2      | 2 | 2   | 2      |

| 7        | 2 | 1 | 2      | 1   | 1      | 1      | 2    | 3     | 1    | 2      | 3      | 3      | 1      | 2 | 2   | 3      |

| 8        | 2 | 1 | 2      | 1   | 2      | 2      | 3    | 1     | 2    | 3      | 1      | 1      | 2      | 3 | 3   | 1      |

| 9        | 2 | 1 | 2      | 1   | 3      | 3      | 1    | 2     | 3    | 1      | 2      | 2      | 3      | 1 | 1   | 2 2    |

| 10       | 2 | 2 | 1      | 1   | 1      | 1      | 3    | 2     | 1    | 3      | 2      | 3      | 2      | 1 | 3   | 2      |

| 11       | 2 | 2 | 1      | 1   | 2      | 2      | 1    | 3     | 2    | 1      | 3      | 1      | 3      | 2 | 1   | 3      |

| 12       | 2 | 2 | 1      | 1   | 3      | 3      | 2    | 1     | 3    | 2      | 1      | 2      | 1      | 3 | 2   | 1      |

| 13       | 1 | 1 | 1      | 2   | 1      | 2      | 3    | 1     | 3    | 2      | 1      | 3      | 3      | 2 | 1   | 2      |

| 14       | 1 | 1 | 1      | 2   | 2      | 3      | 1    | 2     | 1    | 3      | 2      | 1      | 1      | 3 | 2   | 3      |

| 15       | 1 | 1 | 1      | 2   | 3      | 1      | 2    | 3     | 2    | 1      | 3      | 2      | 2      | 1 | 3   | 1      |

| 16       | 1 | 2 | 2      | 2   | 1      | 2      | 3    | 2     | 1    | 1      | 3      | 2      | 3      | 3 | 2   | 1      |

| 17       | 1 | 2 | 2      | 2   | 2      | 3      | 1    | 3     | 2    | 2      | 1      | 3      | 1      | 1 | 3   | 2      |

| 18       | 1 | 2 | 2      | 2   | 3      | 1      | 2    | 1     | 3    | 3      | 2      | 1      | 2      | 2 | 1   | 3      |

| 19       | 2 | 1 | 2      | 2   | 1      | 2      | 1    | 3     | 3    | 3      | 1      | 2      | 2      | 1 | 2   | 3      |

| 20       | 2 | 1 | 2      | 2   | 2      | 3      | 2    | 1     | 1    | 1      | 2      | 3      | 3      | 2 | 3   | 1      |

| 21       | 2 | 1 | 2      | 2   | 3      | 1      | 3    | 2     | 2    | 2      | 3      | 1      | 1      | 3 | 1   | 2      |

| 22       | 2 | 2 | 1      | 2   | 1      | 2      | 2    | 3     | 3    | 1      | 2      | 1      | 1      | 3 | 3   | 2      |

| 23       | 2 | 2 | 1      | 2   | 2      | 3      | 3    | 1     | 1    | 2      | 3      | 2      | 2      | 1 | 1   | 3      |

| 24<br>25 | 2 | 2 | 1<br>1 | 2 3 | 3<br>1 | 1 3    | 1 2  | 2     | 2 2  | 3      | 1 3    | 3<br>1 | 3      | 2 | 2 2 | 1 2    |

| 25<br>26 | 1 | 1 | 1      | 3   | 2      | 3<br>1 | 3    | 2     | 3    | 3<br>1 | 3<br>1 | 2      | 3<br>1 | 2 | 3   | 3      |

| 20<br>27 | 1 | 1 | 1      | 3   | 3      | 2      | 1    | 3     | 1    | 2      | 2      | 3      | 2      | 3 | 1   | 1      |

| 28       | 1 | 2 | 2      | 3   | 1      | 3      | 2    | 2     | 2    | 1      | 1      | 3      | 2      | 3 | 1   | 3      |

| 29       | 1 | 2 | 2      | 3   | 2      | 1      | 3    | 3     | 3    | 2      | 2      | 1      | 3      | 1 | 2   | 1      |

| 30       | 1 | 2 | 2      | 3   | 3      | 2      | 1    | 1     | 1    | 3      | 3      | 2      | 1      | 2 | 3   | 2      |

| 31       | 2 | 1 | 2      | 3   | 1      | 3      | 3    | 3     | 2    | 3      | 2      | 2      | 1      | 2 | 1   | 1      |

| 32       | 2 | 1 | 2      | 3   | 2      | 1      | 1    | 1     | 3    | 1      | 3      | 3      | 2      | 3 | 2   |        |

| 33       | 2 | 1 | 2      | 3   | 3      | 2      | 2    | 2     | 1    | 2      | 1      | 1      | 3      | 1 | 3   | 2 3    |

| 34       | 2 | 2 | 1      | 3   | 1      | 3      | 1    | 2     | 3    | 2      | 3      | 1      | 2      | 2 | 3   | 1      |

| 35       | 2 | 2 | 1      | 3   | 2      | 1      | 2    | 3     | 1    | 3      | 1      | 2      | 3      | 3 | 1   | 2      |

| 36       | 2 | 2 | 1      | 3   | 3      | 2      | 3    | 1     | 2    | 1      | 2      | 3      | 1      | 1 | 2   | 3      |

The presence of two noise factors, the gate oxidation temperature and polysilicon oxidation temperature, was meant to put the undesirable effect (temperature) into design consideration. The values of noise factors at different levels are listed in Table 2. The function of an orthogonal array is to reduce the number of experiments in identifying the most dominant factors in the design. The data produced from the experiment will be studied by using the S/N and ANOVA analysis. The  $L_{36}$  ( $3^{16}$ ) orthogonal array consists of 36 sets of experiment. The experimental layout of the  $L_{36}$  ( $3^{16}$ ) orthogonal array for the input process parameters is shown in Table 3.

#### RESULTS AND DISCUSSION

After the process simulation was done using the ATHENA module, the designed device was then characterized utilizing the ATLAS module. In this section, the electrical characteristics of the first set of experiments will be discussed. Finally, the optimization approach using the Taguchi method is discussed in detail.

## **Device Characterization**

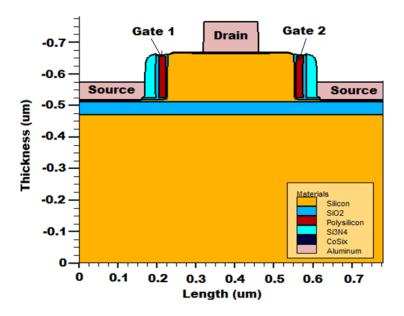

Figure 2 shows the graph of the subthreshold drain current ( $I_D$ ) versus gate voltage ( $V_G$ ) at drain voltage  $V_D = 0.05V$  and  $V_D = 1.0V$  for the SOI vertical DG-MOSFET device. The value of off-leakage current ( $I_{OFF}$ ) and drive current ( $I_{ON}$ ) can be extracted from the graph. From the graph, it is observed that the value of the drive current ( $I_{ON}$ ) was at 474  $\mu$ A/ $\mu$ m. The high drive current ( $I_{ON}$ ) is required for high-speed switching operation. The  $I_{ON}$  is the maximum drain current ( $I_{DMAX}$ ) when  $V_{GS} = V_{DD}$  and  $V_{DS} = V_{DD}$ . Meanwhile, the off-leakage current ( $I_{OFF}$ ) was observed to be at 0.024 x 10<sup>-9</sup> A/  $\mu$ m. The  $I_{OFF}$  is defined as a drain-to-source current and it is measured when  $V_{GS} = 0$  and  $V_{DS} = V_{DD}$ . In other words, the off-state current ( $I_{OFF}$ ) is the drain current when no gate voltage is applied. The off-leakage current ( $I_{OFF}$ ) was the electrical characteristic that had been optimized by using the Taguchi method.

Figure 2. Graph of subthreshold drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>).

# **Leakage Current (Ioff) Acquisition**

The experimental results for  $I_{OFF}$  in the SOI Vertical DG-MOSFET device are shown in Table 4. Each set of experiments produced four different  $I_{OFF}$  values due to the presence of two noise factors, which are factor U (gate oxidation temperature) and factor V (polysilicon oxidation temperature).

Table 4. I<sub>OFF</sub> values for SOI Vertical DG-MOSFET device.

| Experiment no. |                     | Leakage Curren | t, I <sub>OFF</sub> (nA/µm) |                     |

|----------------|---------------------|----------------|-----------------------------|---------------------|

|                | $I_{\mathrm{OFF1}}$ | $I_{ m OFF2}$  | $I_{ m OFF3}$               | $I_{\mathrm{OFF4}}$ |

|                | $(U_1V_1)$          | $(U_1V_2)$     | $(U_2V_1)$                  | $(U_2V_2)$          |

| 1              | 0.024               | 0.017          | 0.020                       | 0.014               |

| 2 3            | 12.965              | 9.108          | 11.027                      | 7.49                |

| 3              | 7799.56             | 5704.11        | 7202.73                     | 5234.88             |

| 4              | 0.027               | 0.020          | 0.022                       | 0.016               |

| 5              | 3.722               | 2.450          | 3.128                       | 2.092               |

| 6              | 7096.08             | 4826.54        | 6520.6                      | 4349.59             |

| 7              | 0.259               | 0.184          | 0.201                       | 0.142               |

| 8              | 1044.71             | 717.9          | 900.67                      | 638.0               |

| 9              | 1.298               | 0.775          | 1.073                       | 0.662               |

| 10             | 42.661              | 22.998         | 36.374                      | 18.758              |

| 11             | 0.070               | 0.045          | 0.057                       | 0.037               |

| 12             | 297.33              | 224.70         | 264.64                      | 199.79              |

| 13             | 576.65              | 425.39         | 507.22                      | 372.93              |

| 14             | 0.946               | 0.523          | 0.808                       | 0.442               |

| 15             | 0.253               | 0.148          | 0.192                       | 0.111               |

| 16             | 482.03              | 345.76         | 418.98                      | 297.89              |

| 17             | 1.234               | 0.728          | 1.041                       | 0.615               |

| 18             | 0.318               | 0.219          | 0.256                       | 0.174               |

| 19             | 0.029               | 0.022          | 0.025                       | 0.019               |

| 20             | 287.05              | 209.61         | 256.36                      | 185.29              |

| 21             | 22.985              | 12.753         | 18.763                      | 10.234              |

| 22             | 11.423              | 7.076          | 9.046                       | 5.975               |

| 23             | 8331.52             | 5985.85        | 7669.64                     | 5480.76             |

| 24             | 0.017               | 0.012          | 0.014                       | 0.01                |

| 25             | 298.31              | 220.02         | 261.72                      | 197.37              |

| 26             | 16.58               | 8.529          | 12.799                      | 7.01                |

| 27             | 0.052               | 0.04           | 0.045                       | 0.035               |

| 28             | 121.01              | 87.213         | 105.61                      | 75.471              |

| 29             | 12.506              | 6.758          | 9.985                       | 5.313               |

| 30             | 0.076               | 0.045          | 0.064                       | 0.038               |

| 31             | 6575.38             | 4703.25        | 5863.8                      | 4307.13             |

| 32             | 0.022               | 0.016          | 0.017                       | 0.012               |

| 33             | 20.504              | 13.763         | 17.33                       | 11.519              |

| 34             | 1.571               | 0.853          | 1.321                       | 0.727               |

| 35             | 0.22                | 0.15           | 0.177                       | 0.117               |

| 36             | 515.85              | 372.67         | 449.27                      | 322.55              |

Table 5. Mean sum of SQ and S/N ratio for I<sub>OFF</sub>.

| Exp no. | Mean sum of SQ | S/N ratio               |

|---------|----------------|-------------------------|

| -       |                | (lower-the-better) (dB) |

| 1       | 0.0004         | 34.374                  |

| 2       | 107.19         | -20.301                 |

| 3       | 4E+07          | -76.351                 |

| 4       | 0.0005         | 33.305                  |

| 5       | 8.5042         | -9.2963                 |

| 6       | 3E+07          | -75.286                 |

| 7       | 0.0404         | 13.939                  |

| 8       | 706262         | -58.49                  |

| 9       | 0.9688         | 0.1379                  |

| 10      | 1005.9         | -30.026                 |

| 11      | 0.0029         | 25.397                  |

| 12      | 62211          | -47.939                 |

| 13      | 227458         | -53.569                 |

| 14      | 0.5042         | 2.9742                  |

| 15      | 0.0338         | 14.714                  |

| 16      | 154046         | -51.877                 |

| 17      | 0.8787         | 0.5618                  |

| 18      | 0.0612         | 12.131                  |

| 19      | 0.0006         | 32.383                  |

| 20      | 56597          | -47.528                 |

| 21      | 286.93         | -24.578                 |

| 22      | 74.521         | -18.723                 |

| 23      | 5E+07          | -76.86                  |

| 24      | 0.0002         | 37.393                  |

| 25      | 61212          | -47.868                 |

| 26      | 140.15         | -21.466                 |

| 27      | 0.0019         | 27.239                  |

| 28      | 9774.7         | -39.901                 |

| 29      | 82.5           | -19.165                 |

| 30      | 0.0033         | 24.769                  |

| 31      | 3E+07          | -74.709                 |

| 32      | 0.0003         | 35.328                  |

| 33      | 260.71         | -24.162                 |

| 34      | 1.3673         | -1.3587                 |

| 35      | 0.029          | 15.379                  |

| 36      | 177717         | -52.497                 |

## Signal-to-noise (S/N) Response Analysis

After the results of 36 experiments have been obtained by utilizing SILVACO TCAD tools, the next step is to implement S/N response analysis. The objective of the S/N response analysis is to determine the signal-to-noise ratio (SNR) for every input process parameter. The SNR is used to determine the optimal input process parameters and analyse the experimental data. For the S/N response analysis for  $I_{OFF}$ , the category of the lower-the-better is selected due to its ability to reduce the response value to the minimum possible. The SNR (lower-the-better),  $\eta$  can be expressed as [11]:

$$\eta = -10Log_{10} \left[ \frac{1}{n} \sum_{i=1}^{n} y_i^2 \right]$$

(1)

where n is the number of tests and yi is the experimental value of  $I_{OFF}$ . The S/N ratio (lower-the-better) of each experiment was computed and recorded in Table 5 [11].

The effect of each input process parameter on the S/N ratio at different levels was separated because the experimental design is orthogonal. The S/N ratio (SNR) for each of the process parameters is summarized in Table 6. Normally, a larger SNR will result in a lower value of leakage current (I<sub>OFF</sub>). In addition, the overall mean SNR for the 36 experiments was also calculated and listed in Table 6. Basically, a larger S/N ratio will result in better quality characteristics for the leakage current [4]. The higher the quality characteristic value to the target, the better the device quality will be [6]. It is crucial that effort must be focused on reducing the sensitivity to noise by optimizing the SNR.

Symbol **Process Parameter** S/N ratio (lower-the-better) Level 1 Level 2 Level 3 Substrate Implant Dose -14.72 -16.5 A В V<sub>TH</sub> Implant Dose -16 -15.22C V<sub>TH</sub> Implant Energy -16.08-15.14D V<sub>TH</sub> Implant Tilt -17.54 -14.41 -14.87 E Polysilicon Doping Dose -20.11 -17 -9.713F Polysilicon Doping Energy 2.7877 -9.271 -9.713 G Polysilicon Doping Tilt 21.042 -22.29-45.58 Η Halo Implant Dose -14.75-15.2-16.87J Halo Implant Energy -21.24 -11.59 -13.99K Halo Implant Tilt -10.79 -16.07-19.97L S/D Implant Dose -14.5 -22.38 -9.94 M S/D Implant Energy -16.23 -20.03 -10.57N S/D Implant Tilt -8.726 -15.04-23.07O Compensation Implant Dose -15.05 -22.63 -9.152 P Compensation Implant Energy -19.34 -10.42-17.06 Q Compensation Implant Tilt -16.39 -21.84 -8.603

Table 6. S/N response for I<sub>OFF</sub>.

# **Analysis of Variance (ANOVA)**

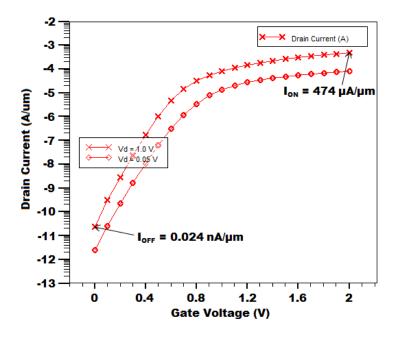

The objective of the analysis of variance (ANOVA) is to find out which input process parameters have the most significant impact on the leakage current (I<sub>OFF</sub>). Basically, it computes parameters called sum of squares (SS), degrees of freedom (DF), variance, F-value and percentage of each factor. The results of ANOVA for the SOI Vertical DG-MOSFET device are shown in Table 7. According to these analyses, the most dominant factors for SNR are factor G (Polysilicon doping tilt=59%) and factor F (Polysilicon doping energy=25%). Therefore, these factors should be set at 'best setting'.

Table 7. Results of ANOVA for IOFF.

| Process parameters | DF | SS    | MS    | F-value | Factor effect on SNR (%) |

|--------------------|----|-------|-------|---------|--------------------------|

| A                  | 1  | 28    | 28    | 60      | 0                        |

| В                  | 1  | 5     | 5     | 11      | 0                        |

| C                  | 1  | 8     | 8     | 17      | 0                        |

| D                  | 2  | 69    | 34    | 73      | 0                        |

| E                  | 2  | 648   | 3421  | 722     | 1                        |

| F                  | 2  | 11885 | 5943  | 12548   | 25                       |

| G                  | 2  | 27436 | 13718 | 28966   | 59                       |

| Н                  | 2  | 30    | 15    | 32      | 0                        |

| J                  | 2  | 606   | 303   | 640     | 1                        |

| K                  | 2  | 509   | 255   | 538     | 1                        |

| L                  | 2  | 951   | 475   | 1004    | 2.04                     |

| M                  | 2  | 544   | 272   | 574     | 1                        |

| N                  | 2  | 1240  | 620   | 1309    | 3                        |

| 0                  | 2  | 1095  | 547   | 1156    | 2                        |

| P                  | 2  | 516   | 83    | 545     | 1                        |

| Q                  | 2  | 1062  | 129   | 1121    | 2                        |

Figure 3. Pareto plot of I<sub>OFF</sub> for SOI Vertical DG-MOSFET device.

Meanwhile, the remaining factors will be considered as neutral or negligible factors. Therefore, they do not have a large effect on the output response. The neutral factors level can be adjusted if the leakage current (I<sub>OFF</sub>) value is not as small as expected. The percentage of a factor's effect on SNR indicates the priority of that factor (process parameter) to reduce variation. The Pareto plot of the standardized effect of I<sub>OFF</sub> for the SOI Vertical DG-MOSFET device is shown in Figure 3. The Pareto plot compares the

relative magnitude and the statistical significance of all the main effects and ranks of the parameters accordingly. From Figure 3, it is obvious that the output response I<sub>OFF</sub>, factor G (Polysilicon doping tilt=59%) and factor F (Polysilicon doping energy=25%) are the most significant parameters. Since factor G and factor F were fixed to level 1, the other input process parameters were varied in order to get the optimum result. After a few adjustments to the level of the process parameters, the best level setting of the process parameters was identified as A1, B2, C2, D2, E1, F1, G1, H1, J2, K1, L1, M3, N1, O1, P1 and Q3. Factors A, B, C, D, E, F, G, H, J, K, L, M, N, O, P and Q respectively represent the substrate implant dose, V<sub>TH</sub> implant dose, V<sub>TH</sub> implant energy, V<sub>TH</sub> implant tilt, polysilicon doping dose, polysilicon doping energy, polysilicon doping tilt, halo implant dose, halo implant energy, halo implant tilt, S/D implant dose, S/D implant energy and compensation implant tilt.

# Confirmation Experiment for Response, IOFF

The confirmation experiment is used to verify the expected results with the experimental results. The best setting of input process parameters for the SOI Vertical DG-MOSFET device which were suggested by the Taguchi method is shown in Table 8. The confirmation experiment is required in the device design because the optimum combination of parameters and their levels, i.e. A1, B2, C2, D2, E1, F1, G1, H1, J2, K1, L1, M3, N1, O1, P1 and Q3, do not correspond to any experiment of the orthogonal array.

| Symbol | Process parameter              | Units                | Best Value            |

|--------|--------------------------------|----------------------|-----------------------|

| A      | Substrate Implant Dose         | atom/cm <sup>3</sup> | $1x10^{14}$           |

| В      | V <sub>TH</sub> Implant Dose   | atom/cm <sup>3</sup> | $3.81 \times 10^{11}$ |

| C      | V <sub>TH</sub> Implant Energy | keV                  | 12                    |

| D      | $V_{TH}$ Implant Tilt          | degree               | 10                    |

| E      | Polysilicon Doping Dose        | atom/cm <sup>3</sup> | $3.60 \times 10^{14}$ |

| F      | Polysilicon Doping Energy      | keV                  | 20                    |

| G      | Polysilicon Doping Tilt        | degree               | 7                     |

| H      | Halo Implant Dose              | atom/cm <sup>3</sup> | $1.17 \times 10^{13}$ |

| J      | Halo Implant Energy            | keV                  | 172                   |

| K      | Halo Implant Tilt              | degree               | 24                    |

| L      | S/D Implant Dose               | atom/cm <sup>3</sup> | $1.22 \times 10^{18}$ |

| M      | S/D Implant Energy             | keV                  | 47                    |

| N      | S/D Implant Tilt               | degree               | 74                    |

| O      | Compensation Implant Dose      | atom/cm <sup>3</sup> | $2.51 \times 10^{12}$ |

| P      | Compensation Implant Energy    | keV                  | 61                    |

| Q      | Compensation Implant Tilt      | degree               | 13                    |

Table 8. Best setting of process parameters.

The result of the final simulation for the device is shown in Table 9. Before the optimization approaches, the best SNR (lower-the-better) is 37.393 dB at row 24 of the experiment (see Table 5). After the optimization approaches, the SNR (lower-the-better) of the leakage current (I<sub>OFF</sub>) for the SOI Vertical DG-MOSFET device is 39.44 dB, which is higher than any of the values in Table 5. Hence, it is proven that the selected level of input process parameters is the optimum level setting (the highest SNR). In addition, these values are still within the predicted range. For the S/N ratio (lower-the-better), 39.44 dB

is within the predicted S/N ratio range of 19.73 to 59.15 dB (39.44  $\pm$  19.71 dB). These indicate that the Taguchi method is able to predict the optimum solution in finding the SOI Vertical DG-MOSFET device fabrication recipe with the lowest leakage current value. The leakage current ( $I_{OFF}$ ) value for the device was afterwards observed to be 0.009 nA/µm or 9 pA/µm, as highlighted in Table 9. This leakage current ( $I_{OFF}$ ) value was observed to be the lowest value among all the experiments done before.

Table 9. Results of confirmation experiments for I<sub>OFF</sub>.

| Le                | akage curren      | SNR (lower-the-better) |            |          |

|-------------------|-------------------|------------------------|------------|----------|

| I <sub>OFF1</sub> | I <sub>OFF2</sub> | I <sub>OFF3</sub>      | $I_{OFF4}$ |          |

| $(U_1V_1)$        | $(U_1V_2)$        | $(U_2V_1)$             | $(U_2V_2)$ |          |

| 0.016             | 0.012             | 0.013                  | 0.009      | 39.44 dB |

#### CONCLUSIONS

In conclusion, the optimum solution in designing the SOI Vertical DG-MOSFET device with the lowest leakage current (I<sub>OFF</sub>) value was successfully predicted by utilizing the L<sub>36</sub> orthogonal array (OA) of the Taguchi method. Leakage current (I<sub>OFF</sub>) is the main response studied in this project as it is one of the main factors that affect the power consumption of the device. The leakage current (I<sub>OFF</sub>) must be as low as possible while keeping the drive current (I<sub>ON</sub>) value at a high level. This will result in a higher I<sub>ON</sub>/I<sub>OFF</sub> ratio, thereby lowering the power consumption of the device. Taguchi method design is used to develop a systematic design of experiment. It has many variants that can be applied to model the device and a lot of input process parameters can be analysed. The level of significance of each input process parameter on the leakage current (I<sub>OFF</sub>) is determined by using ANOVA. Based on the ANOVA method, the most dominant input process parameters on leakage current (I<sub>OFF</sub>) were factor G (polysilicon doping tilt=59%) and factor F (polysilicon doping energy=25%). The leakage current (I<sub>OFF</sub>) value after the optimization approach was 0.009 nA/μm or 9 ρA/μm, while keeping the drive current  $(I_{ON})$  value at  $4\overline{34} \mu A/\mu m$ . Both the drive current  $(I_{ON})$  and leakage current  $(I_{OFF})$  values yield a higher I<sub>ON</sub>/I<sub>OFF</sub> ratio (48.22 x 10<sup>6</sup>) for lower power consumption application.

#### **ACKNOWLEDGEMENTS**

The authors would like to thank to the Ministry of Higher Education (MOHE) and Centre for Telecommunication Research and Innovation (CeTRI), Faculty of Electronics and Computer Engineering (FKEKK), Universiti Teknikal Malaysia Melaka (UTeM) for sponsoring this research study under the research grants (PJP/2014/FKEKK(6B)/S01341) and FRGS(RACE)/2012/FKEKK/TK02/02/2 F00148.

## **REFERENCES**

- [1] Vinay Kumar Yadav AKR. Impact of Channel Doping on DG-MOSFET Parameters in Nano Regime-TCAD Simulation. International Journal of Computer Applications. 2012;37:36-41.

- [2] Roy K, Mukhopadhyay S, Mahmoodi-Meimand H. Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits. Proceedings of the IEEE. 2003;91:305-27.

- [3] Mead C. Scaling of MOS technology to submicrometer feature sizes. Analog Integrated Circuits Signal Process. 1994;6:9–25.

- [4] Esme U. Application of Taguchi Method for the Optimization of Resistance Spot Welding Process. The Arabian Journal for Sciences and Engineering. 2009;30.

- [5] Salehuddin F, Ahmed I, Hamid FA, Zaharim A, Elgomati HA, Majlis BY, Apte PR. Optimization of HALO Structure Effects in 45nm p-type MOSFETs Device Using Taguchi Method. World Academy of Science, Engineering and Technology. 2011;51:1136-42.

- [6] Naidu NVR. Mathematical model for quality cost optimization. Proc International Conference on Flexible Automation and Intelligent Manufacturing. 2008. p. 811-5.

- [7] Abdullah H, Jurait J, Lennie A, Nopiah ZM, Ahmad I. Simulation of fabrication process VDMOSFET transistor using Silvaco software. European Journal of Scientific Research. 2009;29:461-70.

- [8] Yang K, Teo EC, Fuss FK. Application of Taguchi method in optimization of cervical ring cage. International journal of Biomechanics. 2007;40:3251-6.

- [9] Kaharudin KE, Hamidon AH, Salehuddin F. Impact of Height of Silicon Pillar on Vertical DG-MOSFET Device. International Journal of Computer, Information, Systems and Control Engineering. 2014;8:576-80.

- [10] Elgomati HA, Ahmed I, Salehuddin F, Hamid FA, Zaharim A, Majlis BY, Apte PR. Optimal solution in producing 32nm CMOS technology transistor with desired leakage current. International Journal Semiconductor Physics Quantum Electron Optoelectron. 2011;14:145-51.

- [11] Phadke MS. Quality engineering using robust design: Pearson Education, Inc. and Dorling Kindersley Publishing, Inc; 2001.